China oficializó el 17 de febrero de 2026 la producción en masa de los primeros chips electrónicos híbridos no binarios. Esta avance industrial combina lógica binaria y probabilista, enfocándose en la inteligencia artificial, la aviación y sistemas inteligentes, con una promesa clara: mayor eficiencia energética.

Las limitaciones energéticas y arquitectónicas del binario frenan la evolución de los procesadores modernos

Desde los inicios de la informática, los procesadores se han basado en 0 y 1. Esta lógica simple estructura todos los cálculos. Sin embargo, la lógica binaria tradicional muestra hoy sus límites, ya que consume mucha energía y complica la integración con sistemas antiguos.

En Pekín, el profesor Li Hongge, de la Universidad Beihang, señala un doble bloqueo energético y arquitectónico. Según él, los chips actuales generan demasiado calor y requieren muchos recursos. Además, su diseño rígido dificulta la adaptación a nuevos usos, lo que lleva a la industria a buscar una alternativa viable.

La lógica probabilista abre un camino más flexible pero ralentiza el procesamiento de datos complejos

Para superar estos bloqueos, el equipo chino explora una lógica probabilista aplicada a los circuitos. En este modelo, la señal ya no representa estrictamente 0 o 1. Por el contrario, depende de una frecuencia medida en el tiempo, permitiendo así cálculos más flexibles.

Gracias a este enfoque, el hardware necesario se reduce y el consumo eléctrico disminuye. Ya se está implementando en el procesamiento de imágenes avanzadas y en algunas redes neuronales. Sin embargo, esto prolonga el tiempo de cálculo; por lo tanto, la potencia de procesamiento bruto puede verse afectada.

En la práctica, se logra una mayor eficiencia energética, pero se sacrifica velocidad pura. Esta limitación frena su adopción masiva, por lo que los ingenieros buscan un compromiso viable para la industria.

El sistema híbrido HSN combina rapidez binaria y eficiencia probabilista en una arquitectura innovadora

En el centro de este avance se encuentra el sistema número estocástico híbrido. Esta arquitectura fusiona ambas lógicas para mantener la rapidez del binario, mientras aprovecha la eficiencia energética del probabilista. Gracias a este equilibrio, se abre un nuevo camino industrial.

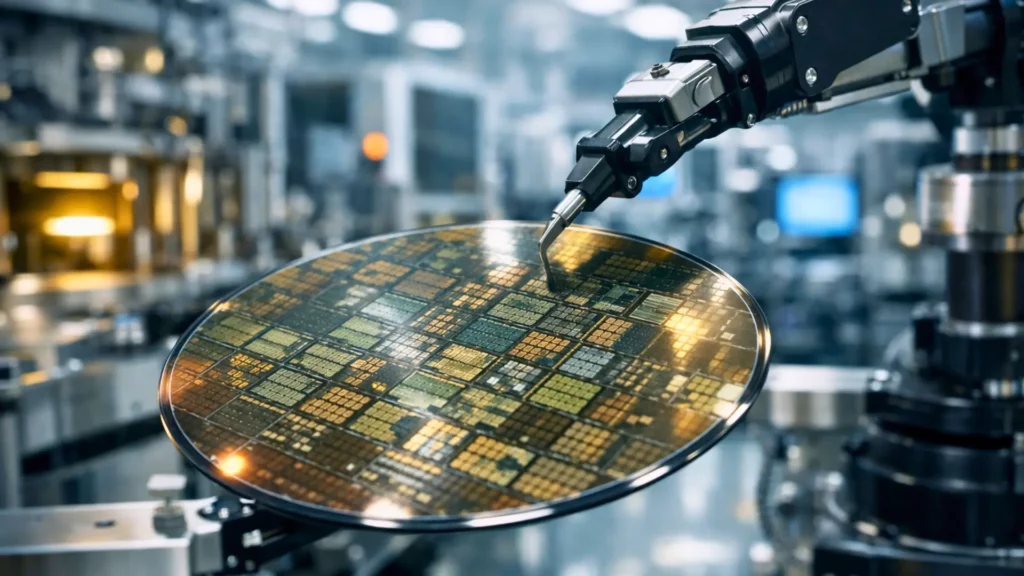

En la práctica, los chips son más tolerantes a fallos y reducen su consumo eléctrico. Además, se adaptan mejor a usos inteligentes. Los primeros modelos, fabricados en 110 nanómetros por SMIC, están dirigidos a chips de pantalla y táctiles innovadores.

Además, en 2023, el equipo lanza una versión dedicada al aprendizaje automático, grabada en 28 nanómetros, que incorpora algoritmos de cálculo en memoria. De este modo, limita las transferencias de datos, acelera el procesamiento y reduce el consumo energético.

Aplicaciones ya activas y un desafío estratégico importante para la industria china de semiconductores

Hoy en día, estos chips equipan sistemas de control inteligente. De hecho, filtran ruido de fondo y detectan señales débiles en pantallas táctiles, logrando latencias de cálculo en microsegundos, mientras mantienen flexibilidad en el software y estabilidad.

Al mismo tiempo, este avance se produce en un contexto geopolítico tenso. Pekín busca reducir su dependencia tecnológica. Con una producción en masa nacional, China refuerza su posición en el sector de semiconductores y ofrece una alternativa viable a las arquitecturas tradicionales dominantes.